CMOS integrovaný širokopásmový LNA zosilňovač s jedným vstupom – teoretické aspekty a simulačná fáza návrhu – 2.časť

05. August, 2013, Autor článku: Maceková Ľudmila, Elektrotechnika

Ročník 6, číslo 8  Pridať príspevok

Pridať príspevok

![]() Návrh zosilňovača v dvojdielnom príspevku je orientovaný na budúcu realizáciu v technológii 0,35 μm SiGe BiCMOS rakúskej firmy AMS. Teoretické podklady, uvedené v minulej – prvej časti, a simulácie obvodovej štruktúry s viac alebo menej ideálnymi komponentmi sú nevyhnutnou súčasťou návrhu integrovaného obvodu. Návrh obvodových štruktúr ako aj simulácie, uvedené v tejto časti, boli uskutočnené v softvérovom balíku ICstudio (Mentor Graphics). Uvedené sú aj výsledky simulácií a ich porovnanie s hodnotami parametrov publikovanými v literatúre.

Návrh zosilňovača v dvojdielnom príspevku je orientovaný na budúcu realizáciu v technológii 0,35 μm SiGe BiCMOS rakúskej firmy AMS. Teoretické podklady, uvedené v minulej – prvej časti, a simulácie obvodovej štruktúry s viac alebo menej ideálnymi komponentmi sú nevyhnutnou súčasťou návrhu integrovaného obvodu. Návrh obvodových štruktúr ako aj simulácie, uvedené v tejto časti, boli uskutočnené v softvérovom balíku ICstudio (Mentor Graphics). Uvedené sú aj výsledky simulácií a ich porovnanie s hodnotami parametrov publikovanými v literatúre.

B. Kaskódové zapojenie

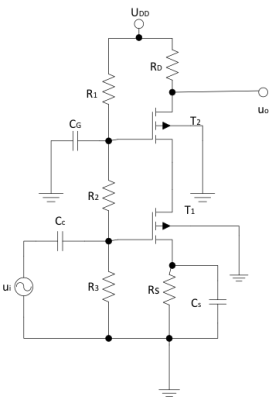

Kaskódové zapojenie (Obr. 7) je často využívaným zapojením s viacerými tranzistormi vo vysokofrekvenčných zosilňovačoch. Kombinuje výhody zapojenia CS (vysoký vstupný odpor a veľký napäťový zisk; tranzistor T1) a zapojenia CG (Common Gate – spoločné hradlo; nasta-viteľná výstupná impedancia, funkcia prúdového buffra a zvýšená medzná frekvencia; tranzis-tor T2) [3].

Obr. 7 Kaskódové zapojenie zosilňovača s tranzistormi MOS-FET

Zvýšenie medznej frekvencie zapojenia je dosiahnuté elimináciou Millerovho efektu. Mil-lerov efekt ako zväčšenie ekvivalentnej vstupnej kapacity CM (medzi G a zemou pri zapojení CS) sa prejavuje v dôsledku kapacitnej väzby medzi vstupom a výstupom (premosťovacia parazitná kapacita CGD) približne podľa vzťahu:

| (30) |

kde RL je zaťažovací odpor takéhoto zapojenia (medzi D a zemou). Pri kaskódovom zapojení priama kapacitná väzba medzi vstupom a výstupom zosilňovača neexistuje. Zaťažovaciu impedanciu tranzistora T1 v zapojení CS tvorí vstupná impedancia tranzistora T2 v zapojení CG, čo je približne rovné 1/gm1 (keď ro v saturácii považujeme za nekonečný). Z toho ekvivalentná vstupná kapacita kaskódy je:

| (31) |

čo je menej než ekvivalentná vstupná kapacita CM vo vzťahu (30). Medzná frekvencia fT závisí od vstupnej kapacity (resp. od časovej konštanty vstupnej impedancie) obvodu nepriamo úmerne:

| (32) |

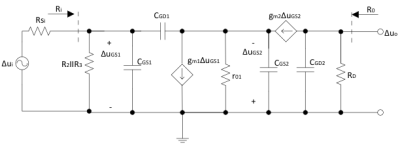

Vysokofrekvenčná náhradná schéma kaskódy pre malé striedavé signály, obsahujúca parazitné kapacity tranzistorov, je na Obr. 8. Z nej potom po odvodení vyplývajú vzťahy pre medzné frekvencie vstupného a výstupného portu [1]:

Obr.8 Vysokofrekvenčná náhradná schéma kaskódového zosilňovača s tranzistormi MOS-FET

časová konštanta vstupného portu τin:

| (33) |

medzná frekvencia vstupného portu:

| (34) |

časová konštanta výstupného portu:

| (35) |

a medzná frekvencia výstupného portu:

| (36) |

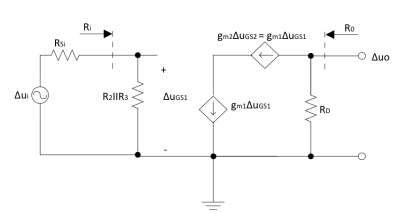

Pre napäťový zisk, vstupný a výstupný odpor kaskódy možno z náhradnej schémy zosilňovača pre malé striedavé signály (na Obr. 9 po zjednodušení) odvodiť nasledujúce vzťahy:

Obr. 9 Náhradný obvod kaskódového zosilňovača pre malé striedavé signály (v pracovnom pásme)

Napäťový zisk

| (37) |

výstupný odpor podobne ako pri jednoduchom zapojení zosilňovača

| (38) |

a vstupný odpor

| (39) |

4. Návrh nesymetrického zosilňovača s MOS-FET

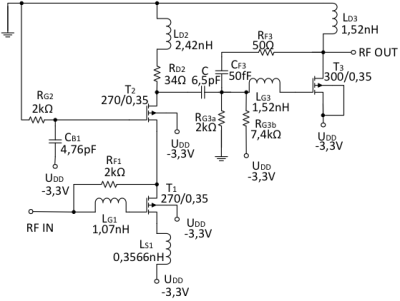

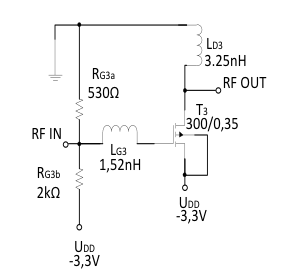

Náš návrh sa uskutočňoval v programe ICstudio. Úvodná štruktúra, ktorá bola inšpirovaná kaskódovým zosilňovačom publikovaným v [2], bola navrhnutá s ohľadom na požadované napájacie napätie mínus 3,3 V a na dĺžku vodivého kanála 0,35 μm. Obsahovala však ideálne pasívne prvky. Po uspokojivých výsledkoch simulačných analýz tejto poloideálnej štruktúry sme prikročili k adaptácii návrhu s využitím modelov pasívnych prvkov z technológie AMS, ktoré sa v maximálnej možnej miere približujú k realite (Obr.10).

V navrhovanom zosilňovači tvorí jadro kaskódový stupeň T1, T2, na ktorý cez LC obvod naväzuje výstupný stupeň v zapojení CS. Komponenty LG1, LS1 a RF1 riešia vstupné impedančné a šumové prispôsobenie zosilňovača. LC obvody na výstupoch oboch stupňov zvyšujú zisk v celom pásme a induktor LG3 (peaking inductor) pred hradlom výstupného stupňa zväčšuje jeho 3-dB pásmo [2].

Obr. 10 Schéma navrhovaného širokopásmového zosilňovača, zohľadňujúca reálne AMS modely tranzistorov a pasívnych prvkov, ako aj požiadavku napájania

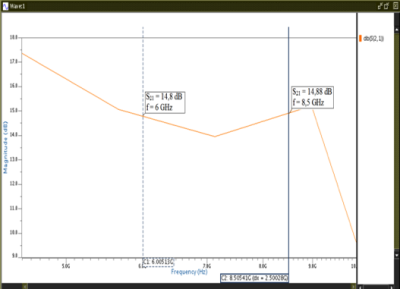

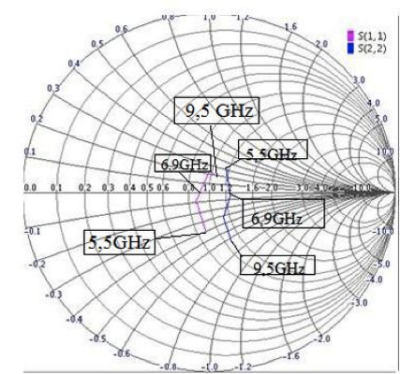

V spomínanom softvérovom balíku od Mentor Graphics sme uskutočnili simulačné analýzy tohto návrhu s modelmi prvkov AMS, a ich výsledky sme porovnali s parametrami zosilňovačov v niektorých publikovaných zdrojoch. Výsledky našich analýz S11, S21 a S22 sú ilustrované na Obr. 11; všetky parametre a výsledky simulačných analýz ako aj porovnania sú uvedené v Tabuľke 1.

Obr. 11 Parametre simulovaného zosilňovača v pásme 6 až 8,5 GHz. Hore: frekvenčná závislosť zosilnenia (S21) zosilňovača (hodnoty S21 sú od 14,88 dB nižšie). Dole: parametre S11 (ružová) a S22 (modrá) v Smithovom diagrame. Krivky zobrazujú vývoj ich komplexného charakteru s frekvenciou. Čím bližšie k stredu (bod 1,0), tým lepšie.

Tab.1 Hodnoty parametrov simulovaného navrhovaného obvodu a ich porovnanie s inými vybranými prácami

| Parameter | Náš návrh | [2] | [5] | [6] |

|---|---|---|---|---|

| Frekvencia (GHz) | 6 – 8,5 | 3,1 – 10,6 | 0,435 | 23,2 |

| S11 (dB) | < -16 | < -9,7 | - | -5 |

| S22 (dB) | < -17 | < -8,4 | - | -3 |

| S21 (dB) | 14 – 15 | 11,4±0,4 | 22 | 13,5 |

| S12 (dB) | < -56 | < -40 | 48 | -30 |

| Šumové číslo (dB) | 3,3 – 5 | 4,12 – 5,16 | 0,6 | 5,9 |

| Spotreba (mW) | 470 | 22,7 | 10 | 55 |

| Napájanie (V) | -3,3 | 1,9 | 2,5 | 3,6 |

| 1-dB kompresný bod (dBm) | -9,5 | -7,86 | -12,5 | -7 |

| Technológia CMOS | 0,35 μm | 0,18 μm | 0,35 μm SOI | 0,18 μm |

Z uvedených simulácií možno zatiaľ urobiť nasledovné zhrnutie: Napäťový zisk (S21) vo vyznačenom pásme medzi 6 až 8,5 GHz nadobúda hodnoty od 14 do 14,8 dB. Klesá a rastie maximálne o 0,8 dB. Spätný prenosový koeficient S12, dôležitý pre určenie stability obvodu, v celom pásme nadobúda hodnoty nižšie ako -56 dB, čo je hodnota, ktorá by mohla vyhovovať, vzhľadom k výsledkom opísaným v referenčnej literatúre. Hodnoty odrazového parametra S11 sú menšie než -16 dB a parametra S22 menšie než -17 dB. V požadovanom pásme šumové číslo simulovaného obvodu nadobúda hodnoty 3,3 až 5dB. Kompresný bod, t. j. hodnota vstupného výkonu, pri ktorej dochádza k saturácii simulovaného zosilňovača je -9,5 dBm. Záver z porovnania výsledkov v tabuľke je zatiaľ taký, že by sme sa mohli uberať ďalej touto cestou, t.j. realizáciou navrhovanej obvodovej štruktúry.

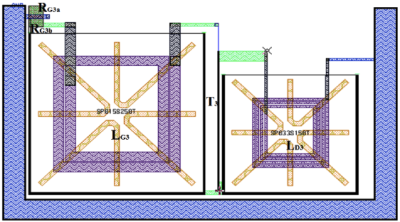

5. Problematika návrhu morfologických masiek pre výrobu integrovaného obvodu

Návrh vrstiev čipu je záležitosť, pri ktorej ešte môže dôjsť k situáciám, kedy je nutné navrhnutú schému alebo koncepciu riešenia prepracovať. Okrem dodržania integrity obvodu a správnosti zapojenia, sú tu ešte ďalšie náročné kroky a činnosti. K nim patrí kontrola a prípadné potlačenie vzniknutých parazitných parametrov, ako aj záležitosti rozmerov a ich proporcií. Na Obr. 12 je ukážka menšej časti nášho zosilňovača “prenesená” do mikroštruktúry v programe ICstudio. Z tohto čiastočného návrhu layoutu už teraz vieme, že keď zahrnieme do návrhu čipu aj induktory, budú práve ony zaberať na čipe najväčšie plochy a budú významnou mierou túto plochu zväčšovať. Takže prinajmenšom tento bod návrhu bude ešte predmetom analýzy a rozhodovania sa medzi touto a inými alternatívami riešenia (externé súčiastky).

Obr. 12 Ilustrácia pomerov plôch špirálových indukčností a ostatných prvkov obvodovej štruktúry zobrazenej hore

Izolačné vzdialenosti, veľkosti metalických plôch, proporcie oblastí tranzistorov ako aj všetkých prvkov a vodičov navrhovaného obvodu, atď., musia vyhovovať požiadavkám konkrétnej technológie výrobcu (tzv. “design rules”), ktoré na tomto čiastočnom morfologickom návrhu zatiaľ ani nie sú zohľadnené. Post-layout simulácie, výroba a testovanie skutočného obvodu by mali nasledovať až po týchto krokoch v budúcnosti.

Záver

Zosilňovač , ktorého návrh bol opísaný v dvoch častiach na pokračovanie, zatiaľ existuje v simulovanej podobe. Vzhľadom na uvedené parametre tohto simulovaného obvodu by sa mohlo v budúcnosti prikročiť k ďalším krokom návrhu, a potom k jeho výrobe.

Poďakovanie

Podporujeme výskumné aktivity na Slovensku/ Projekt je spolufinancovaný zo zdrojov EÚ. Tento článok bol vypracovaný v rámci projektu “Centrum excelentnosti integrovaného výskumu a využitia progresívnych materiálov a technológií v oblasti automobilovej elektroniky”, ITMS 26220120055.

Podporujeme výskumné aktivity na Slovensku/ Projekt je spolufinancovaný zo zdrojov EÚ. Tento článok bol vypracovaný v rámci projektu “Centrum excelentnosti integrovaného výskumu a využitia progresívnych materiálov a technológií v oblasti automobilovej elektroniky”, ITMS 26220120055.

Literatúra

- D. A. Neamen: Microelectronics: Circuit analysis and design. Fourth edition. McGraw-Hill, 2010. ISBN 978-0-07-338064-3

- Ch.-Z. Chen, J.-H. Lee, Ch.-Ch. Chen, Y.-Sh. Lin: An Excellent Phase-Linearity 3.1-10.6 GHz CMOS UWB LNA Using Standard 0.18 gm CMOS Technology, in Proceedings of Asia-Pacific Microwave Conference, 2007.

- J. Dobeš, V. Žalud: Moderní radiotechnika, Techn. literatura BEN, Praha 2006, ISBN 80-7300-132-2.

- P. R. Gray, R. G. Meyer, P. J. Hurst, S. H. Lewis: Analysis and Design of Analog Integrated Circuits, 4th ed. New York, NY, USA: John Wiley & Sons, Inc., 2001

- E. Zencir, N. Dogan, E. Arvas, M. Ketel: A Low-power low-noise amplifier in 0,35 µm SOI CMOS technology, in Circuits and Systems, 2003, ISCAS’03, Proceedings of conference, pp. 293-296.

- D. Dunwell: K-Band Low-Noise Amplifier Design in CMOS Technology, a master thesis, Queen’s University, Kingston, Ontario, Canada, August 2006

Spoluautorom článku je Peter Korenko, Department of Electronics and Multimedia Communications, Faculty of Electrical Engineering and Informatics, Technical University of Košice, Slovak Republic