Technológie 3D integrácie systémov

17. Október, 2016, Autor článku: Balog Peter, Elektrotechnika

Ročník 9, číslo 10  Pridať príspevok

Pridať príspevok

![]() V článku sú prezentované základné technológie 3D integrácie systémov a ich možnosti využitia. Článok popisuje možnosti puzdrenia súčiastok a riešenia multisubstrátových modulov, ktoré sú používané pri 3D integrácií systémov.

V článku sú prezentované základné technológie 3D integrácie systémov a ich možnosti využitia. Článok popisuje možnosti puzdrenia súčiastok a riešenia multisubstrátových modulov, ktoré sú používané pri 3D integrácií systémov.

Úvod

3D integráciou systému sa zabezpečí menší priestor potrebný pre systém, vyššia spoľahlivosť a menšie náklady. Zmenšovaním šírky vodivých dráh, šírky izolačných medzier, veľkosti pokovených dier, veľkosti puzdier súčiastok a rozstupov medzi vývodmi sa dosahuje zvýšená integrácia. Existujú tri hlavné smery predstavujúce koncepčné riešenia 3D integrácie systémov:

- „System on Chip“ (SoC) – všetky obvody, resp. dôležité obvodové funkcie sú integrované na jednom čipe,

- „System in Package“ (SiP) – všetky dôležité funkcie sú integrované do jediného puzdra, ktoré môže obsahovať viacero čipov,

- „System on Module“ (SoM) – všetky dôležité funkcie sú integrované na jednom substráte, ktorý obsahuje príslušné funkčné bloky.

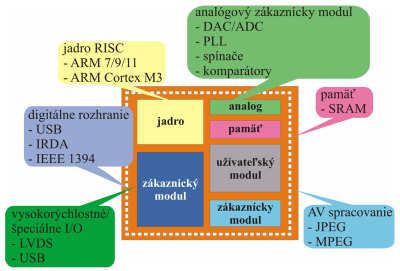

Na Obr. 1 sú zobrazené pokročilé technológie umožňujúce vysokú hustotu 3D integrácie systémov.

Obr. 1 Pokročilé technológie pre vysokú integráciu systémov [1]

1. System on Chip

System on Chip je technológia, ktorá integruje všetky potrebné elektronické obvody systému v jedinom integrovanom obvode (čipe). Napríklad SoC pre zariadenia na detekciu zvuku môžu zahŕňať audio prijímač, A/D prevodník, mikroprocesor, pamäť a potrebné vstupné/výstupné funkcie. Koncepcia System on Chip bola vyvinutá v posledných desiatich rokoch a je ovplyvnená významnými pokrokmi v polovodičovom návrhu a výrobných polovodičových technológiách.

2. System in Package

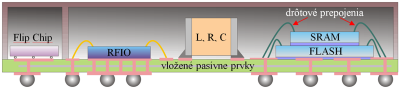

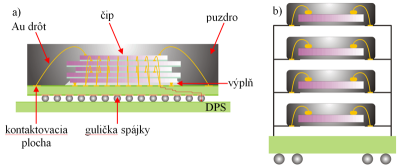

Technologický základ SiP je integrácia jedného alebo viacerých čipov, pasívnych alebo špeciálnych komponentov, vstupov médií (u mikrosystémov), atď., v jednom spoločnom puzdre, ktoré podľa vonkajších podmienok testovania a použitia zodpovedá štandardnému puzdreniu polovodičov. Funkčné časti môžu byť umiestnené vertikálne alebo horizontálne na keramických, polymérnych alebo kovových substrátoch. Kontaktovanie je väčšinou realizované pomocou drôtových kontaktov, ako aj technológiou Flip Chip (Obr. 3).

Z hľadiska rozšírenia použitia SiP sa musia predovšetkým splniť nasledovné požiadavky:

- cenovo dostupné kontaktovacie techniky (napr. „Multilevel Fine-Pitch Wire Bonding“),

- kontakty pre vysoké teploty a agresívne prostredia,

- nízkoteplotné konštrukčné technológie,

- vývoj nových funkčných materiálov,

- vývoj a etablovanie vysokoprecízneho osadzovania súčiastok („Pick and Place“), ako aj pokročilých technológií realizácie kontaktov.

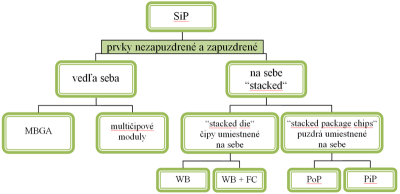

Na Obr. 4 je znázornené základné rozdelenie technológie SiP. V súčasnosti sú pri štandardnom puzdrení realizované tri rôzne typy SiP: „Multichip Module“, „Stacked-Die“, „Stacked-Package“. Často používanými puzdrami sú v tejto súvislosti napríklad QFP, TSSOP, QFN, FBGA. Ďalší typ predstavujú špeciálne vyvinuté puzdrá pre konkrétnu oblasť použitia, pričom sa často používajú technológie priameho pripojenia čipov na rôznych substrátoch.

Obr. 4 Rozdelenie montážnych technológií SiP [2]

Hlavne pri senzorových aplikáciách a mikrosystémoch s prevažne neelektrickými parametrami (mikrooptické, mikrofluidné a pod.) alebo pri systémoch s orientáciou na extrémne oblasti použitia (motorový priestor v aute) sa nutne musia vyvinúť špeciálne technológie pre SiP, kde v popredí stojí funkčné a geometrické prispôsobenie užívateľskému prostrediu. Sem patria napríklad optimalizácia materiálov z hľadiska termomechanických vlastností, vplyv polohovania komponentov, tvorba kontaktov pre väčšie vzdialenosti alebo pre veľké úrovňové rozdiely. V technike mikrosystémov k tomu ešte pristupuje optimálna integrácia rozhraní médií.

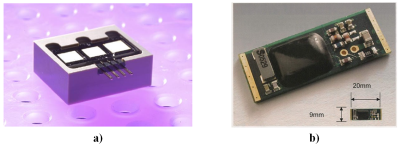

SiP sa vyrábajú hlavne etablovanými technológiami („Fine Pitch“, SMT, „Chip and Wire“, „Flip Chip“, precízne spájkovanie a lepenie, montáž HIO alebo COB) ako subsystémy na planárnych substrátoch. Potom sa subsystémy integrujú do prefabrikovaného puzdra z plastu alebo kovu prispôsobeného oblasti použitia. Následne sa veko zaliatím alebo zalisovaním uzavrie. Na Obr. 5 sú zobrazené príklady použitia SiP v praxi.

Obr. 5 a) Mikroperistaltické čerpadlo pre dlhodobé čerpanie malého množstva analytických tekutín b) SiP pre aplikáciu v medicíne [3]

Trojrozmerné puzdrá môžu byť zostavené z holých alebo zapuzdrených čipov („Stacked Bare Die“, „Stacked Package Chips“). Tento systém tvorí kompaktný celok, ktorý je umiestnený na nosný substrát, určený na pripojenie do systému. Prepojenie do systému takto vytvorenej 3D štruktúry sa realizuje buď spájkovaním štandardných vývodov (BGA, J-Lead, Gull Wing), kontaktovaním („Wire Bonding“) alebo špeciálnou technikou.

Obr. 6 a) Mikroperistaltické Holé čipy v 3D usporiadaní (“Stacked Bare Die“) [4] b) Zapuzdrené čipy v 3D usporiadaní (“Stacked Package Chips“) [5]

2.1. Multisubstrátové moduly (Multisubstrate Modules)

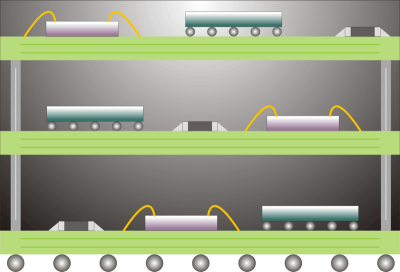

Multisubstrátové moduly sú spravidla riešené spojením keramických alebo organických substrátov osadených súčiastkami v najrôznejších kombináciách. Vzájomné prepojenie substrátov môže byť realizované rôznymi spôsobmi, buď spájkovanými alebo inými prepojmi (drôtové spoje a pod.). Aj v tomto prípade je prepojenie jednotlivých súčiastok realizované rôznymi prepájacími technikami. Súčiastky môžu byť aj vo vyhotovení pre povrchovú montáž.

Obr. 7 3D mikrosystém zložený z rôznych typov puzdier a súčiastok pre povrchovú montáž [5]

2.2. Technológia puzdro na puzdro PoP (Package on Package)

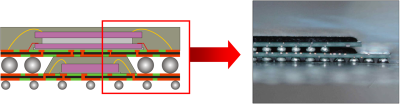

Technológia puzdro na puzdro je technologické riešenie, v ktorom sa testované puzdro ukladá na druhé puzdro počas montážneho procesu a je spojené pomocou guličiek spájky (Obr. 8).

Obr. 8 Technológie vertikálneho ukladania puzdier PoP [6]

2.3. Technológia puzdro v puzdre PiP (Package in Package)

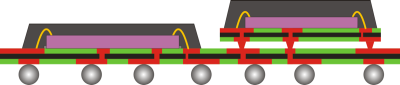

Technológia puzdro v puzdre je iný typ 3D puzdrenia. V tomto riešení nie je vrchné puzdro prepojené so spodným puzdrom pomocou spájkovacích guličiek tak ako PoP, ale namiesto toho je použité veľmi tenké puzdro LGA a spojenie je realizované kontaktovaním tak ako čip (Obr. 9).

Obr. 9 Technológie vertikálneho ukladania puzdier PiP [6]

2.4. MPBGA (Multi Package Ball Grid Array)

MPBGA je riešenie, ktoré integruje multifunkčné komponenty na úrovni puzdra pre zabezpečenie rýchleho a vysokovýkonného riešenia subsystému (Obr. 10). Využíva kontaktovanie, Flip Chip a povrchovú montáž s cieľom umožniť flexibilitu v návrhu a efektivitu vo výrobe.

Obr. 10 MPBGA (Multi Package Ball Grid Array) [7]

3. System on Module

System on Module je usporiadanie systému, pri ktorom sú všetky hlavné funkcie integrované na jednom substráte. Najčastejším využitím princípu System on Module je Computer on Module (CoM), ktorý predstavuje typ jednodoskového počítača. Riešenie System on Module má viacero výhod, ktorými sú rýchlejšie nasadenie na trh, úspora nákladov, menšie riziká vo výrobe, predĺženie životnosti systému, a malé rozmery.

Obr. 11 System on Module pre výpočtovú techniku [8]

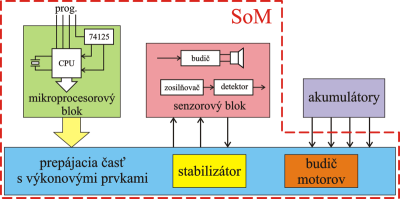

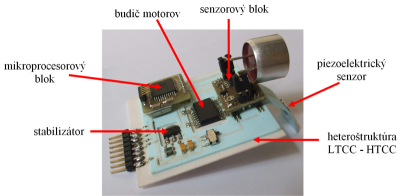

Príkladom aplikácie SoM je konštrukčné riešenie 3D integrácie riadiacej elektroniky mobilného ministroja s využitím heteroštruktúry realizované na KTE FEI. Bloková schéma riadiacej elektroniky zobrazená na Obr. 12 pozostáva z nasledujúcich funkčných blokov – prepájacia časť s výkonovými prvkami (budič motorov a stabilizátor), mikroprocesorový blok a senzorový blok.

Obr. 12 Bloková schéma riadiacej elektroniky mobilného ministroja

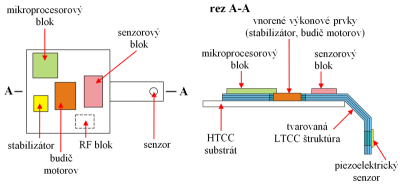

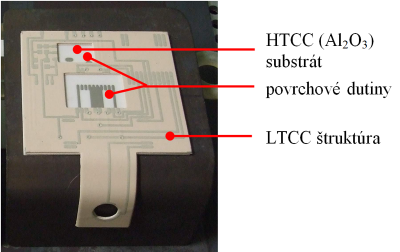

Prepájacia časť je realizovaná na báze heteroštruktúry LTCC štruktúra – HTCC substrát a je na nej integrovaný napájací zdroj so stabilizátorom napätia a budič motorov (Obr. 13), ktoré sú umiestnené na HTCC substráte v povrchových dutinách LTCC štruktúry. HTCC substrát zabezpečuje odvod tepla z výkonových prvkov a mechanické uchytenie v drážkach podvozku ministroja. Na štvorvrstvovej LTCC štruktúre s tvarovanou časťou sú umiestnené nasledujúce funkčné bloky – mikroprocesorový blok, blok senzorovej časti a perspektívne aj blok pre bezdrôtovú komunikáciu.

Obr. 13 Rozmiestnenie funkčných blokov na LTCC štruktúre prepájacej časti [9]

Požadovaný uhol ohybu 90° bol dosiahnutý dvoma samostatnými ohybmi o 45°. Toto riešenie odstraňuje problémy vznikajúce pri ohyboch keramiky v ostrejších uhloch. Po vytvarovaní bola LTCC štruktúra umiestnená na HTCC (Al2O3) substrát na tvarovacom prípravku (Obr. 14) a následne vypálená.

Obr. 14 Heteroštruktúra pripravená na výpal

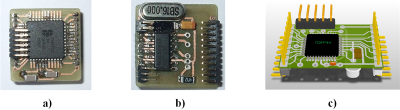

Mikroprocesorový blok je osadený procesorom DS89C430, taktovacím kryštálom s frekvenciou 16 MHz a podpornými obvodmi pre programovanie v systéme. Mikroprocesor obsahuje program na ovládanie motorov, detekciu prekážok a pohybový algoritmus na vyhýbanie sa prekážkam. Mikroprocesorový blok je realizovaný na obojstrannej DPS s rozmermi 20×20 mm.

Obr. 15 Mikroprocesorový blok: a) vrchná strana, b) spodná strana, c) 3D model v programe Altium Designer [10]

Senzorový blok je tvorený obvodmi pre budenie ultrazvukového reproduktora a obvodmi pre príjem, zosilnenie a detekciu signálu a je realizovaný na trojvrstvovej DPS s rozmermi 20×15 mm.

Obr. 16 Blok senzorovej časti: a) vrchná strana, b) 3D model v programe Altium Designer [10]

Prijímací piezoelektrický senzor je umiestnený na tvarovanej LTCC štruktúre prepájacej časti. LTCC štruktúra svojim tvarom zabezpečuje správnu orientáciu senzora voči prekážkam. Použitá koncepcia funkčných blokov umožňuje jednoduchú modifikáciu, prípadne rozšírenie funkcií ministroja. Na Obr. 17 je kompletná integrovaná riadiaca elektronika v zostave SoM.

Obr. 17 Riadiaca elektronika v zostave SoM [9]

Ministroj bol testovaný v laboratórnych podmienkach s analýzou pohybu vpred, vzad, otáčania sa a pohybovej schémy na vyhýbanie sa prekážkam.

Záver

Použitie vhodných technológií 3D integrácií systémov je ovplyvňované rôznymi faktormi. Najdôležitejšími faktormi sú náklady na výrobu, možnosti testovania, limity testovania, dostupnosť komponentov a odvod tepla. Rozhodujúcim faktorom je aj existencia jednotlivých fyzických a informačno-technologických rozhraní.

Zoznam použitej literatúry

- Fujitsu Limited, Semiconductor Solutions. [online]. Dostupné na internete:

http://www.fujitsu.com/emea/services/microelectronics/ - Nunn W., Soido D.: System In Package (SiP) and Stacked Package Solutions, IMAPS, 2007.

- Tremlett P.: SiPin Vivo: System in a Package Enters the Human Body, Advanced microelectronics, Vol. 31, No.1, IMAPS, 2007.

- Renesas Electronics Corporation: SiP, 2014. [online]. Dostupné na internete:

http://www.renesas.com/products/package/trend/sip/index.jsp - Szendiuch I.: Základy technologie mikroelektronických obvodů a systémů, Akademické nakladatelství, VUTIUM, 2006.

- Töpper M., et. al.: WLCSP Technology Direction, Advancing Microelectronics, Vol. 33, No. 1, 2006, pp. 8-11.

- Advanced Semiconductor Engineering Inc.: SiP MPBGA, 2009. [online]. Dostupné na internete:

http://www.asetwn.com.tw/content/2-7-1.html - Atrenta: SoC Realization 2011. [online]. Dostupné na internete:

http://www.atrenta.com/Atrenta-SoC-Realization.pdf - Slosarčík S., Bauer R., Gmiterko A., Cabúk P., Jurčišin M.: Aplikácia nízkoteplotne vypaľovanej keramiky v 3D integrácii systémov, – 2011. In: Chemické listy. Vol. 105, no. S (2011), p. 571-573. – ISSN 0009-2770

- Cabúk P.: Príspevok ku konštrukčným technológiám 3D integrácie systémov, Dizertačná práca, Školiteľ: Slosarčík S., Košice, 2011

Spoluautormi článku sú Michal Jučišin a Stanislav Slosarčík, Katedra technológií v elektronike, Fakulta elektrotechniky a informatiky, Technická univerzita v Košiciach, Park Komenského 2, 040 01 Košice